千、万级逻辑单元的CPLD、FPGA芯片上,设计门之间的组合,设计信号、时钟之间的配合;小到触发器,大到软核操作系统,能小巧玲珑亦能硕大无朋;时而争分夺(纳)秒,时而游手好闲,额,哪里不大对。这些就是我接触到的可编逻辑。

1 准备工作

做了5年设计,大学学的基础知识都快忘光了,难道基础知识和项目经验成反比?诶,别慌,拍个照,发个朋友圈。今天就来回顾下冷宫里的触发器。麻雀虽小五脏俱全,在认识它之前,让我们看看有什么要准备的。

文章中会涉及到时间的概念,希望大家能理解。就算是纳米级的电路,电信号在经过不同长度的导线、不同复杂程度的门电路后,会产生不同程度的延时。延时虽然非常非常小,但没考虑周到的话,千里之堤也会溃于蚁穴。

“ 触发器 ” :一般都是由 “ 与非门 ” 或者“ 或非门 ” 组成的,两者的情况很类似,所以后文用的是 “ 与非门 ” 。 其比较有代表性的 “ RS触发器 ” 、 “ D触发器 ” 也会在文中提到 。

“ 与非门 ” :是一个和 “ 与门 ” 输出结果完全相反的的逻辑门,真值表可以参考百度:与非门 (一种逻辑电路)。

“ 真值表 ” :是通过表格,列出某个模块所有的输入组合对应的输出。输入输出有 “ 0 ” 、 “ 1 ” 、 “ 不稳定状态 ” 、 “ 维持上一个状态不变等情况 ” 。

2 RS触发器

2.1 内部构造

2.2 真值表

| /RD | /SD | Q | /Q |

| 0 | 0 | 不稳定状态 | 不稳定状态 |

| 0 | 1 | 0(==/RD) | 1 |

| 1 | 0 | 1 (==/RD) | 0 |

| 1 | 1 | 保持之前状态 | 保持之前状态 |

- 如果/RD是0,无论Q(G1-B)等于什么,/Q(G2-A)一定是1;这时如果/SD是1,那么Q是0,Q和/Q相反,结果是我们想要的。

- 如果/SD是0,无论/Q(G2-A)等于什么,Q(G1-B)一定是1;这时如果/RD是1,那么/Q是0,Q和/Q相反,结果是我们想要的。

- 如果/SD和/RD都是1,Q(G1-B)和/Q(G2-A)的状态不会发生变化,因为没有新的状态覆盖。

- 如果/SD和/RD都是0,Q(G1-B)和/Q(G2-A)都是1,Q和/Q相同,结果不是我们想要的。Q和/Q相同这种情况,如果直接给到后面的电路使用会出现逻辑问题,所以/SD==/RD==0是个不稳定状态。

我们在电路设计中,除非特殊情况,是不允许使用或者往后级传递不稳定状态的,会给系统带来不稳定因素。所以人们对RS触发器做了适当的改进,如引入了时钟概念的D触发器,其优势在后面介绍脉冲D触发器时介绍。

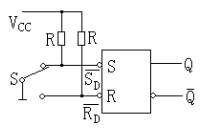

2.3 开关防抖应用

开关的动触头和静触头接触的瞬间会有接触不良现象,数字电路捕获的时候会出现一串高低跳变,这就是开关的抖动。这不是我们想要的,RS触发器可以巧妙的去除这段抖动。

- 当开关接触到/SD侧时,/SD==0,/RD==1,Q==1。

- 当 开关接触到/RD侧时, /SD==1,/RD==0,Q==0。

- 而开关悬空或接触不良的时候, /SD==1,/RD==1,Q保持之前的状态。

3 脉冲D触发器

好了,RS触发器就讲完了,那有的人就要说了,就这?

接下来说说脉冲D触发器。前面提到的RS触发器有个致命的弱点,就是当/RD和/SD都等于0的时候,输出不稳定,所以人们想到了一种解决办法,就是让子弹飞一会儿。嗯,你没听错,就是让子弹飞一会儿。

3.1 内部构造

3.2 真值表

| CP | D | RD | SD | Q | /Q |

| 0 | 0 | 1 | 1 | 保持之前状态 | 保持之前状态 |

| 0 | 1 | 1 | 1 | 保持之前状态 | 保持之前状态 |

| 1 | 0 | 1 | 0 | 1 (==/RD) | 0 |

| 1 | 1 | 0 | 1 | 0 (==/RD) | 1 |

这个真值表的分析方式和前面RS触发器的相似,就不冗述了,感兴趣的可以自己推导一下。通过真值表可以发现,已经没有了不稳定状态,好像一切都万事大吉了,呵呵,那只能说,小伙子,还是年轻了呀。

你们会发现这个D触发器本质还是RS触发器,只是加入了CP这个信号(即时控信号),并且将两个输入端/SD/RD改成了一个输入端D,方便设计人员使用。但它真的和真值表上一样,消除了RS触发器不稳定状态吗?可惜,还是没有。

3.3 不稳定状态 – CP等于1,D从1变成0的过程

| CP | D | RD | SD | Q | /Q |

| 1 | 1 | 0 | 1 | 0 (==/RD) | 1 |

| 1 | 1->0 | 0 | 1 | 0 (==/RD) | 1 |

| 1 | 0 | 0 | 1->0 | 不稳定状态 | 不稳定状态 |

| 1 | 0 | 0->1 | 0 | 1 (==/RD) | 0 |

| 1 | 0 | 1 | 0 | 1 (==/RD) | 0 |

假如目前处于CP==1,D==1,RD==0,SD==1,Q==0;下一刻D从1变成了0,D的0状态通过左下角的与非门到达SD端,使SD==0,这时就会出现SD==RD==0的不稳定现象。而且你会发现,输出的不稳定状态跟输入一点关系没有,纯纯的不稳定。那比较暴躁的小哥就说了,这也不稳定,那也不稳定,这触发器还用不用了。。。

3.4 解决与小结

且看这个CP端,这是一个时钟输入端,通过真值表可知,但凡CP端从1变成0、等于0时,输出端都是稳定状态(保持之前状态),这个可以自己推导一下。那我们何不在CP端变成0后,让后级接收该D触发器的输出Q信号呢?这样每次接收的输出都是稳定的啦,虽然Q会相对于D有所延迟。

这样就万事大吉啦,通过引入一个时钟控制信号,以延迟的代价,解决了触发器的输出不稳定状态,看起来挺完美的。

4 结束语

这种脉冲D触发器真的就完美,便于使用了吗?有想过如何在且仅在CP端变成0后,让后级接收输出Q吗?仔细想想还挺难实现的对吧,那下一篇文章就来解决使用不便的问题,讲讲D触发器的升级版 – 边沿D触发器。

最后附上引用的文章: