(可编逻辑 – RS触发器 D触发器)提到的 “ 脉冲D触发器 ” ,其CP信号等于1时,输出Q会随着输入D的变化而变化,只有当CP等于0才锁定。这虽然产生了一段时间的稳定输出,但只能在CP等于0时做一些操作,难免增加了设计难度。

那下面就来看看升级版 “ 边沿D触发器 ” 是如何化解这个尴尬的吧。

1 上升沿D触发器

1.1 内部构造

1.2 锁存

Data==1被时钟Clock上升沿锁存:

1.3 锁存后的一个时钟周期,新数据准备

锁存之后, Clock ==1时,当输入Data发生变化,输出Q不会发生改变:

锁存之后,Clock==0时,当输入Data发生变化,输出Q不会发生改变:

1.4 新数据再次被锁存

如上一节,Data翻转成0作为新数据,有如下两种稳定状态:

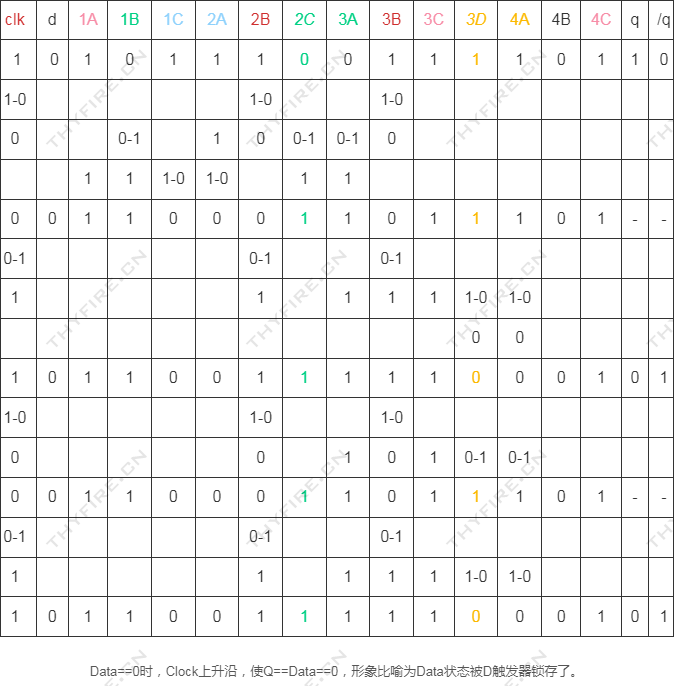

新数据再次被时钟Clock上升沿锁存:

剩下的过程就不冗述了,和前面的推导过程一样。

2 结束语

好啦,今天也不多说啦,总结一下。

“ 上升沿D触发器 ” ,虽然相对 “ 脉冲D触发器 ” 更复杂、占用的资源更多,但其输出Q只在Clock上升沿时发生变化。也就是说,Data只要在Clock上升沿前后保持稳定,我们就可以放心大胆的使用了。得利于这种便捷,我们日常会用它来锁存一些信息,或同步某些信号。

那下一篇就来讲讲 “ 上升沿D触发器 ” 的使用吧,看看有什么需要我们注意的,它又是如何来同步信号的。

最后附上引用的文章:

© 2021-2025 涵涵

本文版权归作者所有,未经作者同意必须在文章页面给出原文连接,否则保留追究法律责任的权利。