“ 边沿D触发器 ” 相较于 “ 脉冲D触发器 ” 有更好的使用性,设计人员只用关注Data在Clock上升沿前后的稳定情况,就可以轻松完成如数据锁存,数据同步等功能。

那Clock上升沿前后如果不稳定,会发生什么呢?让我们来看看吧。

1 相关的概念

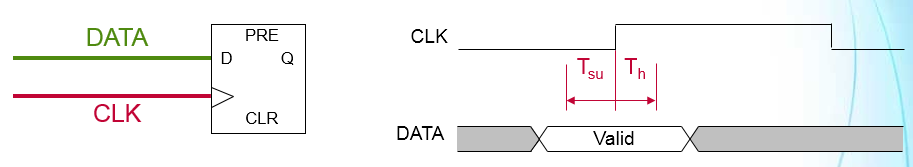

上升沿D触发器的锁存过程并非一蹴而就,而是分为了两个阶段,其一是 “ 数据准备 ” ,其二是 “ 数据锁存 ” 。

“ 数据准备 ” :Data发生跳变,由4B流经一个个与非门,各节点状态逐渐稳定。

“ 数据锁存 ” :时钟Clock上升沿到来,由2B、3B流经一个个与非门,各节点状态逐渐稳定,RS触发器存好Data的值。

“ 建立时间 ” :Tsu,必须大于 “ 数据准备 ” 需要的时间,且留有余量。

“ 保持时间 ” :Th,必须大于 “ 数据锁存 ” 需要的时间,且留有余量。

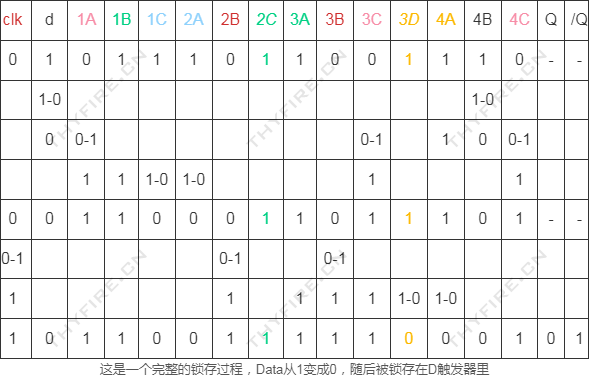

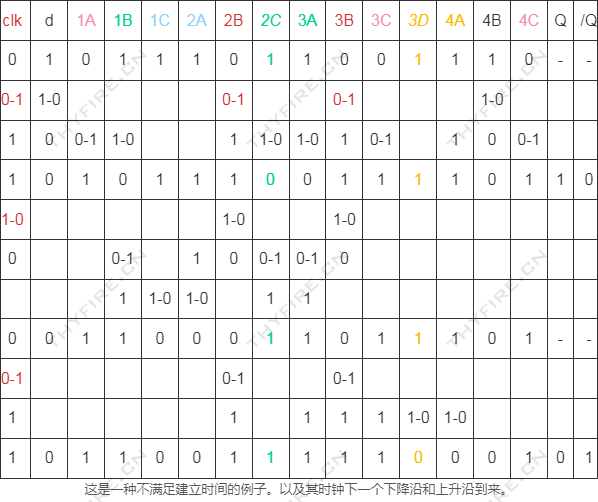

2 建立时间不充足

数据Data还未准备就绪,时钟Clock上升沿提前来了,干扰从2B、3B进入,扰乱了系统。

2.1 过程分析 – 情况1

2.2 过程分析 – 情况2

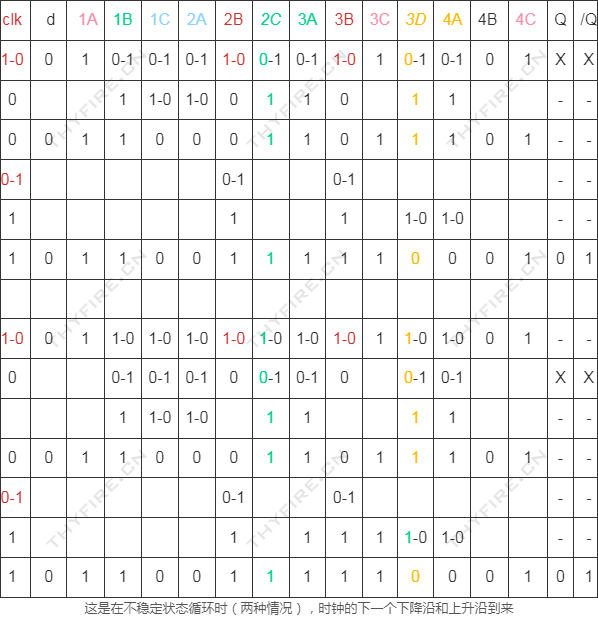

3 保持时间不充足

时钟上升沿的锁存动作未就绪之前,输入数据Data提前跳变,干扰从4B进入,扰乱了系统。

与建立时间类似,这里就不冗述了。

4 总结归纳

在建立保持时间不充足的情况下,从时钟上升沿,到其下降沿(包括保持阶段)之间,会出现锁存错误、不稳定状态等情况;但下一个时钟上升沿到来后,会正确的锁存数据Data的值。

虽然错误只发送在一个时钟周期内,但考虑整个系统的严谨缜密性,原则上所有的边沿D触发器都应该满足其建立保持时间。

5 结束语

今天主要从理论的角度分析了建立保持时间,下一篇文章让我们利用实际的电路和分析报告,看看如何避免问题、优化设计吧。

© 2021-2025 涵涵

本文版权归作者所有,未经作者同意必须在文章页面给出原文连接,否则保留追究法律责任的权利。