我们知道,同步电路中的数据无论何时都与时钟同步,而异步电路中的数据则特立独行、无拘无束。但无论是哪一种,只要工作稳定就是好电路。

但如果我们遇到异步信号需要接入同步电路(如异步信号同步化),这时会遇到什么问题?如何解决?让我们来看看吧。

1 准备工作

“ 同步电路 ” :数据的产生、传递都是由触发器来控制,而触发器的动作由统一的时钟进行管理。

“ 异步电路 ” :区别于同步电路,数据的产生、传递不一定是触发器控制的,且触发器的动作没有统一时钟管理,往往由非时钟信号触发。

“ 异步信号同步化 ” :将异步信号进行一系列处理,然后安全、有效的引入到同步电路的过程。

既然要接入同步电路,就会涉及D触发器及其建立保持时间。我们一般会设计成异步信号接入更高速(如4倍、6倍)时钟的同步电路中,因为这样信号的还原度更高,就算是建立保持时间不充足导致翻转,也不会影响到系统稳定性;另外,会设计多级D触发器作为接口,这样能够在建立保持时间不补充足时,阻止D触发器亚稳定状态进入同步电路。

更高速的时钟我们就不讲了,只需注意比异步信号最高的有效频率更高就行。下面我们来看看多级D触发器如何阻止亚稳定状态传递的。

2 多级D触发器

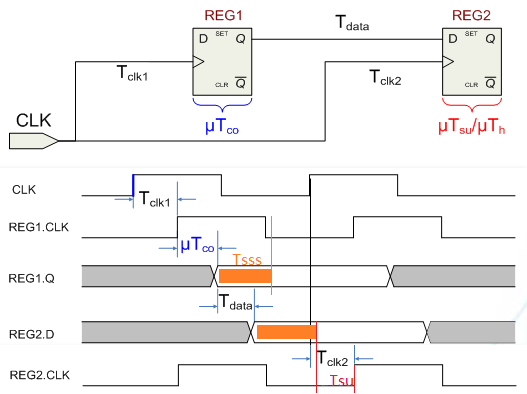

由《可编逻辑 – 建立保持时间2》可知,REG1.D在满足建立保持时间的时候,REG2的 “ 保持时间 ” 等于 Tclk1 + uTco + Tdata – Tclk2, “ 建立时间 ” 等于 T – Th。

由《可编逻辑 – 建立保持时间》可知,如果REG1.D不满足建立保持时间,REG1.Q和REG2.D会出现一段 “ Tsss ” (“ 亚稳定时间 ”),其长度很短,最多会持续半个周期左右。这时建立保持时间会发生变化:

“ 保持时间 ” = Tclk1 + uTco + Tdata – Tclk2,和之前一样,没有发生变化。

“ 建立时间 ” = “ 时钟周期 ” – “ 保持时间 ” – “ 亚稳定时间 ” ,在之前的基础上减小了Tsss,变得更短、更危险了。

3 总结和归纳

3.1 亚稳定状态传递被阻止

通过上面的分析可知,只要 “ 建立富余时间 ” 足够,REG2就不会受到REG1亚稳定状态的影响,并且自己也不会产生亚稳定状态,这样就解决了亚稳定状态向后传递的问题。

还会在设计中看到三级D触发器级联的情况,那可能是建立保持时间设置的不太恰当,或者出于增加系统安全性的考虑,也是可行的。感兴趣的小可爱可以画画时序分析图,自行推导下。

3.2 最大时钟频率变低

有的小可爱会发现, “ 亚稳定时间 ” 加入之后,整个时钟周期可利用的时间变短了,这势必会降低该同步电路的最大时钟频率。感兴趣的可以自行推导一下,需要回顾的见《可编逻辑 – 建立保持时间2》。

3.3 上升沿下降沿灵活运用

原理上讲,只要建立保持富余时间足够,级联的D触发器可以灵活运用同步时钟的上升和下降沿,来提高频率、改变数据与时钟的对齐关系。

4 结束语

设计就是伴随着问题一起成长的。为了自己的目的,克服一个一个的问题和困难,这就是人生的智慧吧。

希望做设计的小伙伴们,遇到问题不要害怕或是放弃,上网看看有没有人遇到过,自己在研究研究、琢磨琢磨,一定能克服哒。

再就是多记笔记,多沉淀文章,这看似没什么用处的举动,在以后会给你带来很大的帮助。